日本TI、高速性と高精度を両立させるSAR ADC「ADC3660ファミリ」を発表

2021/06/10

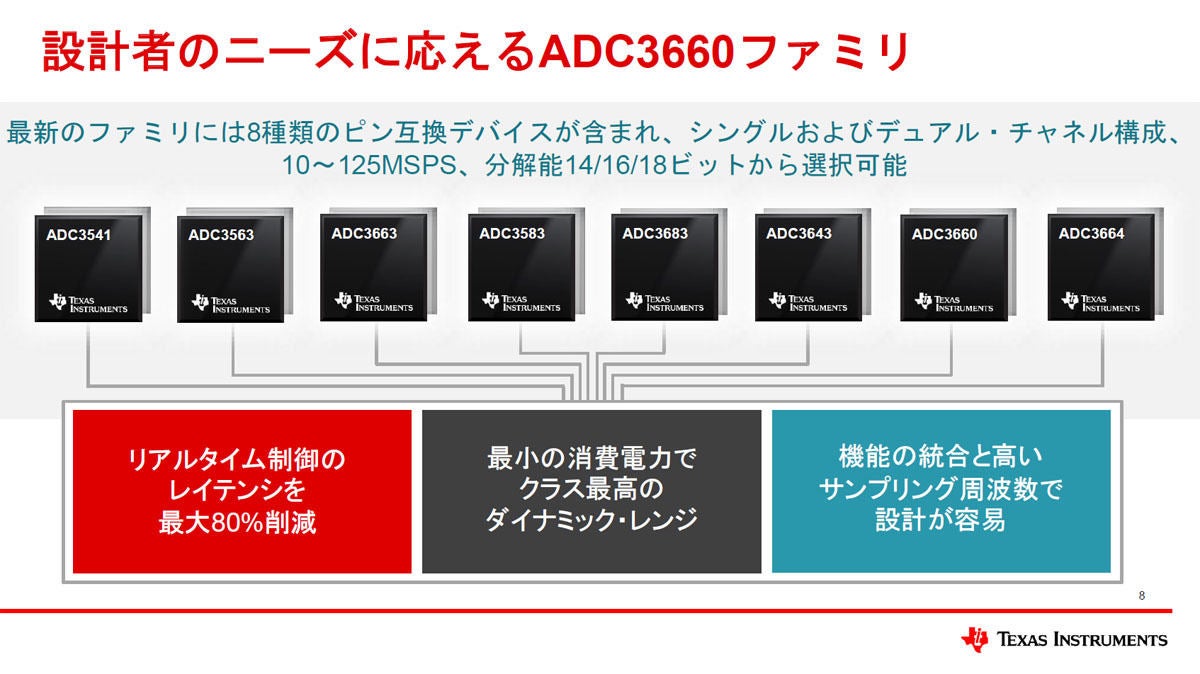

日本テキサス・インスツルメンツ(日本TI)は、産業機器を中心としたリアルタイム制御が要求される高速なデジタル制御ループに対応しつつ、高精度なデータ収集を可能とする逐次比較型(SAR)A/Dコンバータ(ADC)「ADC3660ファミリ」を発表した。

同ファミリは14/16/18ビットの分解能と10~125MSpsのサンプリング速度で8製品が提供される。例えば、14ビットの125MSps、デュアルチャネル品「ADC3664」の場合、1クロック(8ns)のADCレイテンシを実現できると同社では説明しており、ファミリ全体としては、同等速度の競合製品と比較してレイテンシを最大80%短縮できるとしている。

-

ADC3660ファミリのラインアップ (資料提供:日本TI)

同社高速データ・コンバータ製品ライン・マネージャであるマシュー・ハン(Matthew Hann)氏は、「ノイズ性能を取るか、低消費電力性能を取るか、どちらかを優先する必要があった。同ファミリはこうした設計における『正確性』『ノイズ』『電力』『サイズ』『設計時間の短縮』といった課題に対応することを目的に開発されたもので、消費電力を削減しつつ高精度のデータ収集を可能とした製品ファミリとなる」とその位置づけを説明する。例えば、65MSpsの18ビットADC「ADC3683」の場合、競合の18ビットADC製品比でサンプリング速度は4倍、チャネル密度は2倍に向上しており、ポータブル防衛無線などのナローバンド周波数アプリケーションでノイズ性能が向上し、SNRは84.2dB、ノイズ・スペクトル密度は160dBFS/Hzながら、消費電力はチャネルあたり94mWとしている。

-

ADC3660ファミリを活用することによるリアルタイム制御のイメージ (資料提供:日本TI)

低消費電力化としては、従来同クラスのADCではパイプライン型アーキテクチャを採用していたことが電力がなかなか削減できなかった要因であったとし、これを新たにSAR型アーキテクチャに変更することで、実現できたとする。

また、機能が統合も進められており、例えば、設計の複雑さを軽減する機能であるオンチップのデシメーション・オプションを活用することで、設計者はシステムから不要なノイズや高調波を簡単に除去し、SNRとスプリアスフリー・ダイナミック・レンジを最大15dB増強できるようになるという。さらにデジタル・ダウンコンバータならびにフィルタも内蔵しているため、必要とするプロセッサリソースの減少も可能だとしている。加えて、FPGAではなくArmベースのプロセッサまたはDSPを活用することでシステムコストの低減を図ることも可能だとしている。

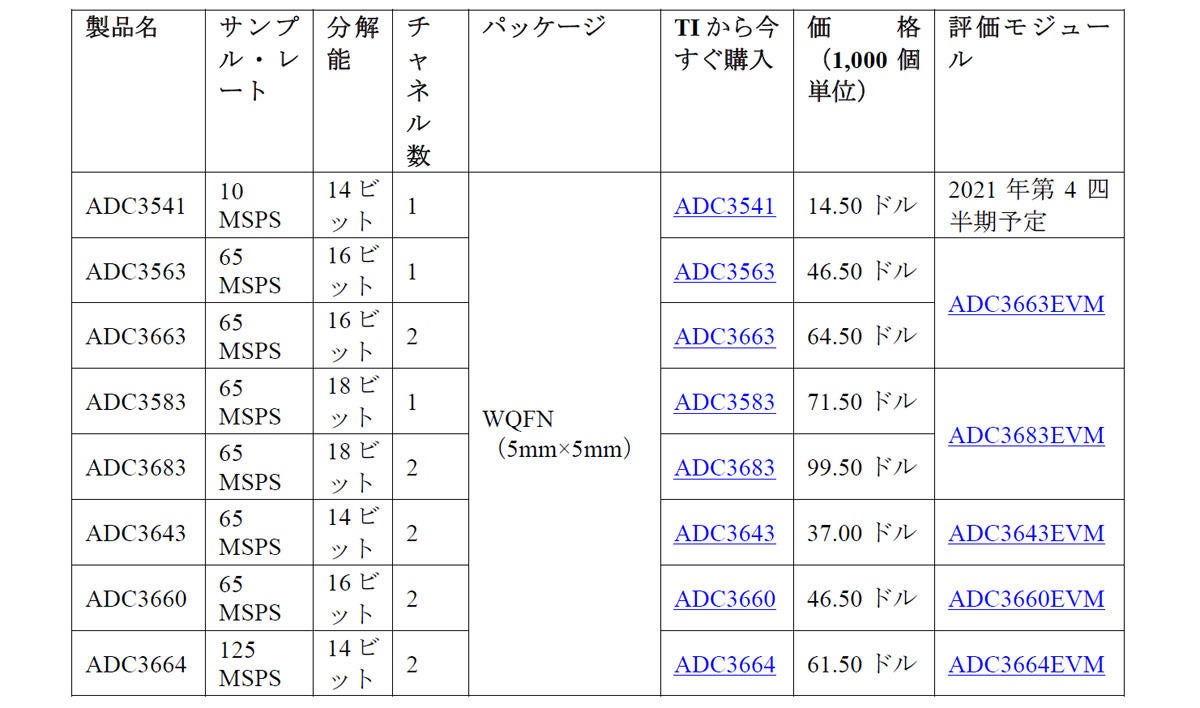

なお、8製品ともに5mm×5mmのWQFNパッケージで同社Webサイト経由で購入が可能(ただし10MSps、14ビット、シングルチャネル品の「ADC3541」のみ量産前バージョンとしての提供。量産は2022年第1四半期を予定)。単価は1000個単位の注文で14.50ドルからとしている、また、評価モジュールも249ドルで提供しているという。

-

8製品の概要 (資料提供:日本TI)

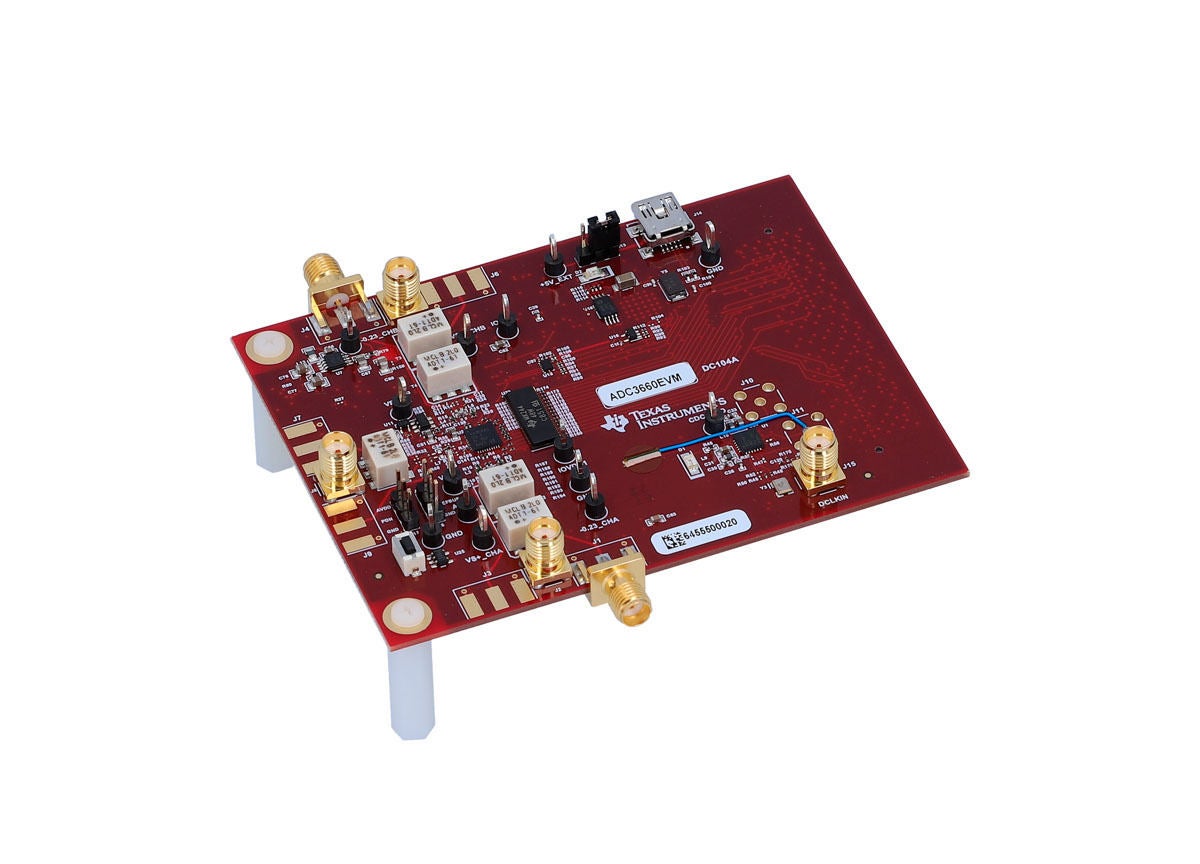

評価モジュールの外観 (画像提供:日本TI)

ソース:日本TI、高速性と高精度を両立させるSAR ADC「ADC3660ファミリ」を発表 | TECH+ (mynavi.jp)